Herausforderungen

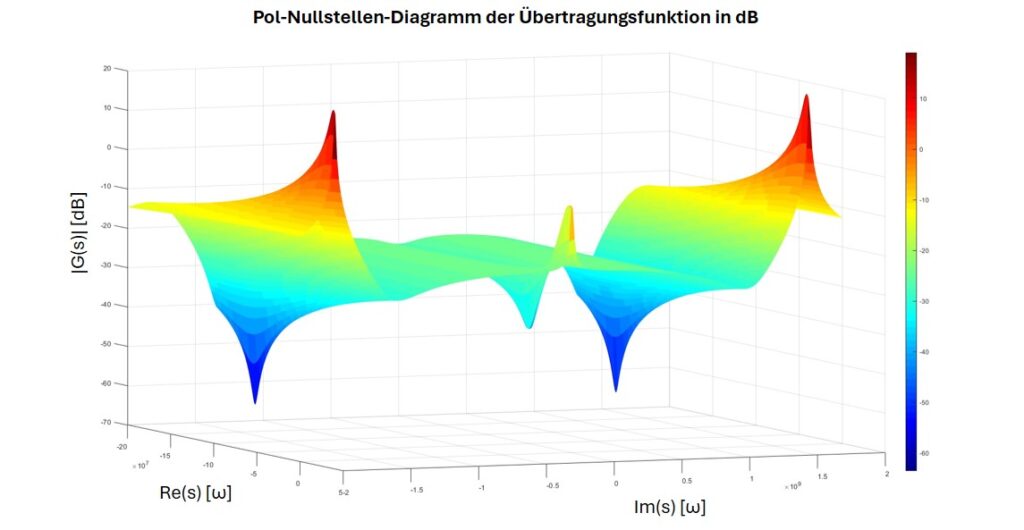

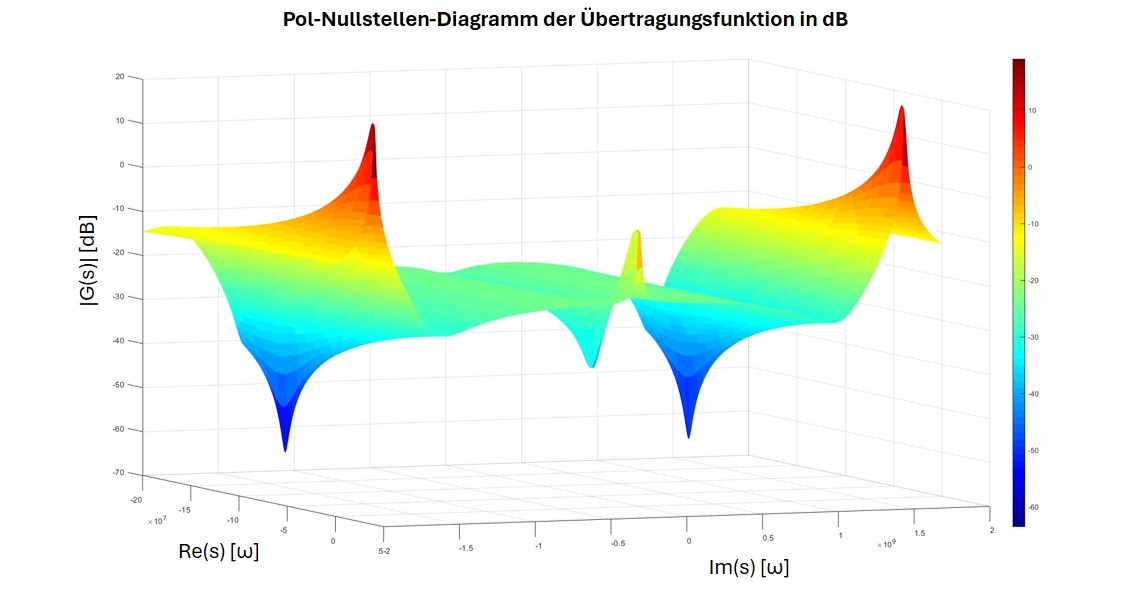

Um höhere Systemleistungen und Wirkungsgrade zu erreichen, werden in der Leistungselektronik häufig viele Transistoren bzw. Leistungshalbleiterchips parallel geschaltet. Dabei entstehen Schwingkreise aus den parasitären Elementen der Leistungshalbleiter und deren aufbau- und schaltungstechnischen Umgebung. Diese Schwingkreise können durch schnelle Schaltflanken angeregt werden, was zu erhöhten Schaltverlusten und Schäden an den Bauelementen führen kann. Im schlimmsten Fall entstehen durch die Verstärkereigenschaft der Transistoren sogar ungedämpfte hochfrequente Oszillationen, die zu einer sofortigen Zerstörung führen können.

Besonders die niedrige Einsatzspannung und hohe Schaltgeschwindigkeit von GaN-HEMTs stellt sehr hohe Anforderungen an das Design und die Implementierung in Leistungsmodule. Um diesen Herausforderungen erfolgreich zu begegnen, ist eine umfassende Systemkenntnis unerlässlich. Im Rahmen unserer Forschungsarbeiten setzen wir auf detaillierte systemtheoretische Analysen und Optimierungen der Schaltungslayouts, um die maximale Performance moderner Leistungshalbleiterbauelemente ausschöpfen zu können.

Forschungsschwerpunkte

- Modellierung und Simulation des Verhaltens parallel geschalteter Transistoren in leistungselektronischen Anwendungen

- Extraktion parasitärer Elemente aus dem Layout von Leistungsmodulen

- Stabilitätsanalyse und Praxistipps für Schaltungslayouts

- Konstruktion und Inbetriebnahme von Umrichtern mit vertikalen und lateralen GaN-Transistoren